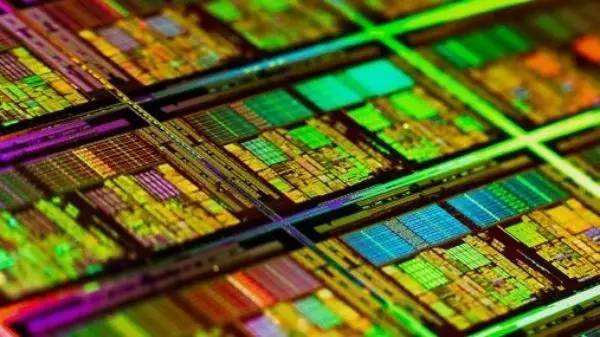

【集成电路】纳米制程是什么?

三星以及台积电在先进半导体制程打得相当火热,彼此都想要在晶圆代工中抢得先机以争取订单,然而半导体制程中所描述的那些数字究竟有何意义?指的又是哪个部位?而在缩小制程后又将来带来什么好处与难题?以下我们将就纳米制程做简单的说明。

纳米到底有多细微?

在开始之前,要先了解纳米究竟是什么意思。在数学上,纳米是 0.000000001 公尺,但这是个相当差的例子,毕竟我们只看得到小数点后有很多个零,却没有实际的感觉。如果以指甲厚度做比较的话,或许会比较明显。

用尺规实际测量的话可以得知指甲的厚度约为 0.0001 公尺(0.1 毫米),也就是说试着把一片指甲的侧面切成 10 万条线,每条线就约等同于 1 纳米,由此可略为想像得到 1 纳米是何等的微小了。

知道纳米有多小之后,还要理解缩小制程的用意,缩小电晶体的最主要目的,就是可以在更小的芯片中塞入更多的电晶体,让芯片不会因技术提升而变得更大;其次,可以增加处理器的运算效率;再者,减少体积也可以降低耗电量;最后,芯片体积缩小后,更容易塞入行动装置中,满足未来轻薄化的需求。

再回来探究纳米制程是什么,以 14 纳米为例,其制程是指在芯片中,线最小可以做到 14 纳米的尺寸,下图为传统电晶体的长相,以此作为例子。缩小电晶体的最主要目的就是为了要减少耗电量,然而要缩小哪个部分才能达到这个目的?左下图中的 L 就是我们期望缩小的部分。藉由缩小闸极长度,电流可以用更短的路径从 Drain 端到 Source 端(有兴趣的话可以利用 Google 以 MOSFET 搜寻,会有更详细的解释)。

IC:纳米制程是什么?

此外,电脑是以 0 和 1 作运算,要如何以电晶体满足这个目的呢?做法就是判断电晶体是否有电流流通。当在 Gate 端(绿色的方块)做电压供给,电流就会从 Drain 端到 Source 端,如果没有供给电压,电流就不会流动,这样就可以表示 1 和 0。(至于为什么要用 0 和 1 作判断,有兴趣的话可以去查布林代数,我们是使用这个方法作成电脑的)

尺寸缩小有其物理限制

不过,制程并不能无限制的缩小,当我们将电晶体缩小到 20 纳米左右时,就会遇到量子物理中的问题,让电晶体有漏电的现象,抵销缩小 L 时获得的效益。作为改善方式,就是导入 FinFET(Tri-Gate)这个概念,如右上图。在 Intel 以前所做的解释中,可以知道藉由导入这个技术,能减少因物理现象所导致的漏电现象。

IC:纳米制程是什么?

更重要的是,藉由这个方法可以增加 Gate 端和下层的接触面积。在传统的做法中(左上图),接触面只有一个平面,但是采用 FinFET(Tri-Gate)这个技术后,接触面将变成立体,可以轻易的增加接触面积,这样就可以在保持一样的接触面积下让 Source-Drain 端变得更小,对缩小尺寸有相当大的帮助。

最后,则是为什么会有人说各大厂进入 10 纳米制程将面临相当严峻的挑战,主因是 1 颗原子的大小大约为 0.1 纳米,在 10 纳米的情况下,一条线只有不到 100 颗原子,在制作上相当困难,而且只要有一个原子的缺陷,像是在制作过程中有原子掉出或是有杂质,就会产生不知名的现象,影响产品的良率。

如果无法想像这个难度,可以做个小实验。在桌上用 100 个小珠子排成一个 10×10 的正方形,并且剪裁一张纸盖在珠子上,接着用小刷子把旁边的的珠子刷掉,最后使他形成一个 10×5 的长方形。这样就可以知道各大厂所面临到的困境,以及达成这个目标究竟是多么艰巨。